CPU의 구조 / 원리

CPU

⸰ 중앙처리장치(Centrol Processing Unit)

⸰ 명령어 해석, 자료의 연산 / 비교 등 처리를 제어하는 핵심장치

⸰ 다양한 입력 장치로 정보를 받아 처리한 후, 결과를 출력 장치로 보내는 모든 과정을 제어, 조정

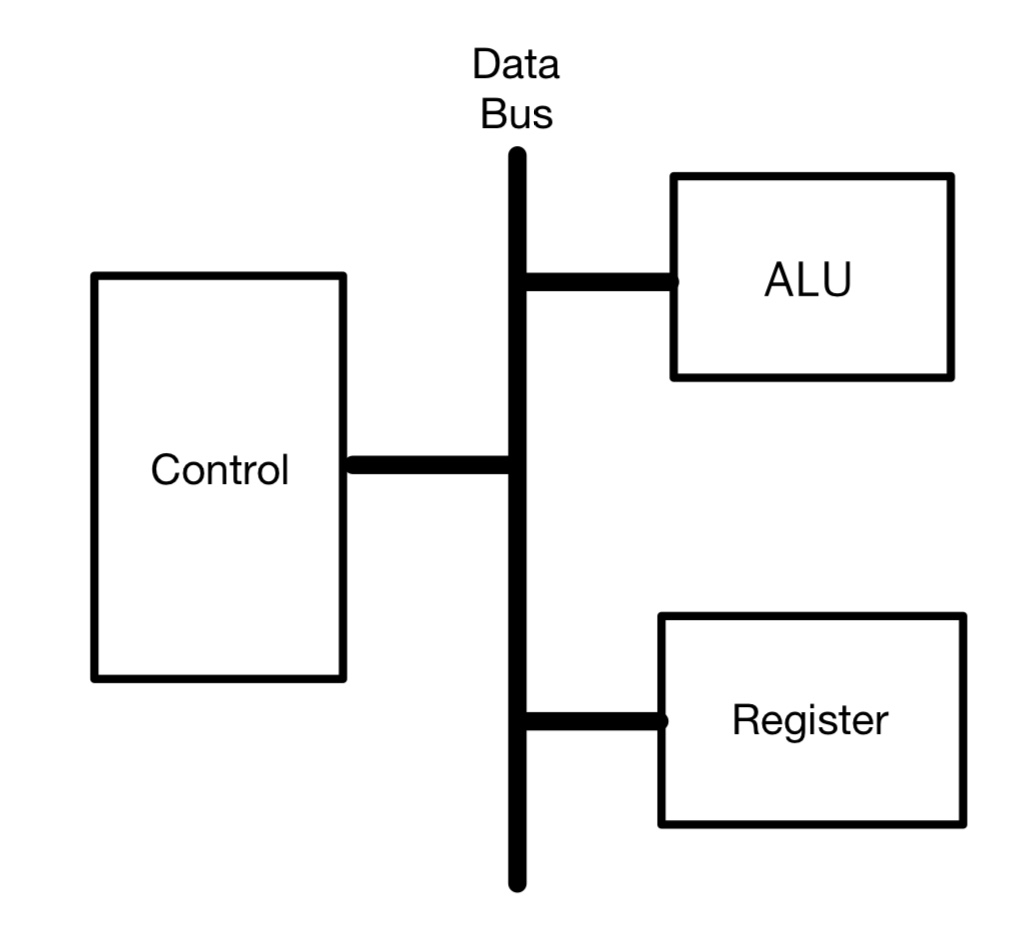

CPU의 구성 요소

⸰ Control Unit(제어 장치), ALU(연산 장치), Register(레지스터)

⸰ 각 요소들은 Data Bus를 통해 데이터를 주고받음

Control Unit(CU, 제어장치)

⸰ CPU 제어하는 장치

⸰ PC(프로그램 카운터), 명령 해독기, 부호기, 명령 레지스터 등 구성

1. ROM(기억 장치)으로부터 프로그램 명령어를 순차적으로 꺼내 해석

2. 어떤 작업을 수행해야 하는지 결정

3. 실행에 필요한 제어 신호를 전달하여 명령 수행

⸰PC

-Program Counter

- 현재 실행 중인 프로그램의 다음 명령어 위치를 가리키는 레지스터

- CPU는 PC가 가리키는 명령어를 실행하고, PC를 증가시켜 다음 명령어의 위치를 가리키며 순차적으로 실행 가능

: 이전 값을 기반으로 다음 값이 카운트되므로, Loadable Counter로 설계돼야 함

⸰MAR

- 메모리 주소 레지스터

- CPU가 메모리에 접근할 주소를 MAR에 저장하고, 이를 통해 메모리와 상호작용 가능

⸰MDR

- 메모리 데이터 레지스터

- 메모리에서 읽어온 데이터, 메모리에 쓸 데이터 임시로 저장

- CPU와 메모리 간 데이터 교환 가능

⸰IR

- 명령어 레지스터

- 현재 실행 중인 명령어를 저장

- CPU는 IR에 저장된 명령어를 디코딩하고 실행

⸰Control Block

- 제어 블록

- CPU 동작을 제어하는 데 사용되는 논리 회로나 레지스터의 집합

- 명령어 실행, 레지스터 간 데이터 이동, 연산 수행 등 CPU 기능 조절, 동기화 가능

- 데이터 버스로 입력되는 데이터들의 전송 신호를 충돌하지 않도록 관리

ALU(Arithmetic and Logical Unit, 연산 장치)

⸰ 명령어 실행을 위한 산술 / 논리 연산 수행

⸰ 결과는 레지스터에 저장되거나 다음 단계로 전달

⸰ 가산기, 누산기, 데이터 레지스터 등 구성

⸰ACC

- 누산기

- CPU 내부에 위치한 레지스터 중 하나

- CPU 명령어에 따라 데이터 읽어오고, 연산의 중간 결과를 저장

⸰BREG

- 버퍼 레지스터

- 데이터를 임시로 저장하고 전송하는 레지스터

- 데이터의 안정적인 전송과 처리를 도움

Register(레지스터)

⸰ CPU 내부에 위치한 소규모 고속 기억 장치

⸰ 명령어 주소, 코드 연산에 필요한 데이터 / 연산 결과 등 임시로 저장

⸰ 메모리 계층 최상위에 위치, 가장 빠른 속도

⸰ 범용 레지스터, 특수 목적 레지스터로 구분

⸰TMPREG

- Temporary Register

- 일시적으로 데이터 저장하고 처리하는 레지스터

- CPU 연산 동안 임시 데이터 스토리지로 사용

⸰CREG

- Control Register

- 시스템 제어, 설정을 관리하는 레지스터

- 시스템 설정, 모드 전환, 예외 처리 / 중요한 제어 동작 수행

- 프로세서 모드 변경, 인터럽트 활성화 / 비활성화, 보안 관리

⸰RREG

- General-Purpose Register

- 일반 목적 레지스터

- 다양한 연산 / 데이터 저장

- 프로그램 카운터, 스택 포인터, 범용 데이터 저장

- 주로 직접 접근하여 데이터 조작

⸰OUTREG

- Output Register

- 데이터 출력과 관련된 작업 수행하는 레지스터

- 입출력 연산, 데이터 전송, 디스플레이 제어 / 통신

- 외부장치와 데이터 주고받음

CPU의 동작 원리

1.Fetch(인출) : 메모리상 프로그램 카운터가 가리키는 명령어를 CPU로 인출하여 레지스터에 적제

2.Decode(해석) : 명령어 해석하여 명령어의 종류, 타깃 등 판단

3.Execute(실행) : 해석된 명령어에 따라 데이터 연산 수행

4.Writeback(쓰기) : 명령어대로 처리 완료된 데이터를 메모리에 기록

명령어 사이클

1. 인출 사이클 : 항상 수행

2. 실행 사이클 : 항상 수행

3. 간접 사이클 : 주소 지정방식 필요 시

4. 인터럽트 사이클 : 인터럽트 요구 발생 시

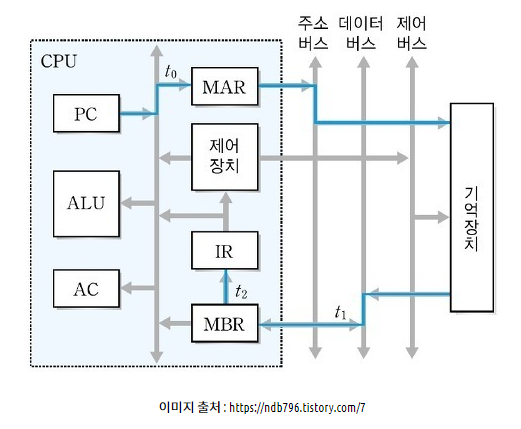

Fetch Cycle(인출 과정)

1. 프로그램 카운터에 저장된 주소를 MAR(주소)로 전달

2. MAR(주소)에 저장된 내용으로 주기억장치의 해당 주소에서 명령어를 인출

3. 인출한 명령어를 MBR(버퍼)에 저장

4. 다음 명령어를 인출하기 위해 PC 값 증가

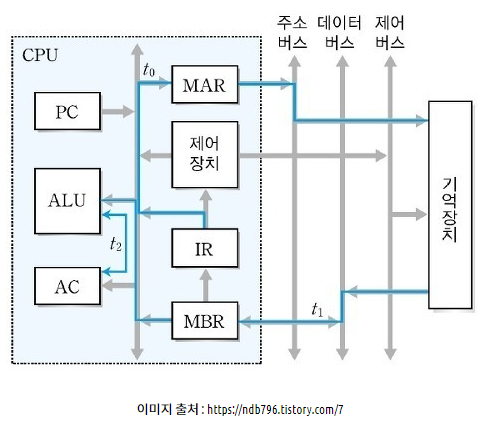

Execute cycle(실행 과정)

1. IR(명령어) 내용을 MAR(주소)로 전달

2. 메모리에 저장된 데이터를 MBR(버퍼)에 저장

3. 명령어 종류에 따라 ALU, 데이터 이동, 입출력 등 명령한 연산 수행

'💠기타 > 컴퓨터 과학 (CS)' 카테고리의 다른 글

| [컴파일러] 컴파일러의 구조 (0) | 2024.09.02 |

|---|---|

| [네트워크] TCP 연결 해제할 때, 포트를 바로 닫지 않는 이유는? (0) | 2024.08.07 |

| [CS50] 「3」 스크래치(엔트리), C언어 자료형 (1) | 2024.06.11 |

| [CS50] 「2」 의사 코드, 정렬, 탐색, 시간 복잡도 (2) | 2024.06.11 |

| [CS50]「1」 컴퓨터, 진수, 가상 현실/증강 현실, 인공지능 (4) | 2024.06.11 |